## UNIVERSITÉ DE BOUMERDES MASTER 1 INFOTRONIQUE SEMESTRE 2

## DEPARTEMENT D'INFOTRONIQUE E 2 SYSTEMES NUMERIQUES COMPLEXES TRAVAUX DIRIGES 4 (1H30)

#### **EXERCICE 1:**

Considérez le système d'équations logiques suivant :

$$P = ABCD + \bar{B}\bar{D} + \bar{A}\bar{C}D + E\bar{F}G$$

$$O = BC + A\bar{B} + \bar{C}D$$

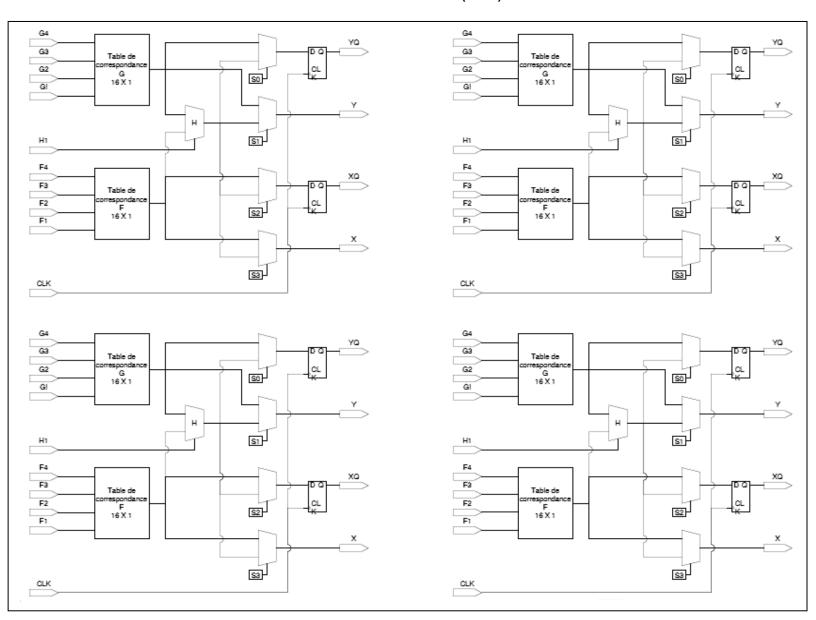

Considérez le circuit montré à la page 3, qui représente une portion d'un réseau prédiffusé programable (FPGA) général. En utilisant ce circuit, montrez comment implémenter ce système d'équations.

- Indiquez clairement la position de chaque port, le contenu des tables de correspondance (Look-Up Table – LUT) et le routage des différents signaux.

- 2. Considérez l'extrait de code VHDL suivant. Donnez son équivalent en matériel à l'aide d'un schéma de portes logiques.

## **EXERCICE 2:**

Soit le code VHDL suivant.

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity MAC is

generic (W: positive := 4);

port (

clk,rst: in std_logic;

entree1, entree2, entree3: in signed(W-1 downto

0);

sortie: out signed(2*W downto 0));

end MAC;

```

a - Donnez le diagramme du circuit MAC correspondant au code VHDL ci-avant. Indiquez la largeur en bits des ports et des signaux intermédiaires en sachant que W est égal à 4. Vous pouvez utiliser des opérations logiques et arithmétiques, la comparaison, des multiplexeurs, décodeurs et encodeurs, éléments mémoire, etc.

```

library ieee;

use ieee.std_logic_1164.all;

entity exo1 is

port (

A,B,C: in std_logic;

F,G,H: out std_logic);

end exo1;

architecture arch of exo1 is

begin

F <= not(A and (B xor not(C)));

G <= '0' when (A = '1' or B /= C) else '1';

with A select H <= B when '0', C when others;

end arch;

```

```

architecture beh of MAC is

begin -- beh

sortie <= (entree1 * entree2) + entree3;

end beh;

```

- b Donnez le diagramme du circuit itératif combinatoire à 3 étages qui cascade 3 MAC en sachant que le port entree3 du premier étage de MAC prendra la valeur zéro. En sachant que le port entree3 du prochain étage prendra la valeur du port sortie du module de l'étage précédent.

- c Donnez le diagramme du circuit itératif séquentiel de 3 étages qui cascade 3 MAC. En sachant que le port entree3 du premier étage de MAC sera prendra la valeur zéro.

#### **TRAVAUX DIRIGES 4 (1H30)**

## **EXERCICE 3:**

Soit l'entité module3 ainsi que le banc d'essai module3 the permettant de le vérifier. Les codes VHDL de ces modules sont comme suit:

```

library ieee;

library IEEE;

use ieee.std logic 1164.all;

use IEEE.std logic 1164.all;

use ieee.numeric std.all;

entity module3TB is

end module3TB;

entity module3 is

architecture arch of module3TB is

port (

component module3

A, B: in std logic;

port (

F: out std logic

A, B: in std logic;

F: out std logic

end module3;

architecture arch of module3 is

end component;

signal S1, S2: std_logic;

begin

signal A,B,F: std logic;

S_1 \leq A and B;

begin

S2 \leq not(B);

UUT: module3 port map (A, B, F);

A <= '0' after 0 ns, '1' after 20 ns;

process (S1, S2)

B <= '1' after o ns, '0' after 10 ns,

begin

F \leq S1 \text{ xor } S2;

'1' after 15 ns;

end process;

end arch;

end arch;

```

Donnez le chronogramme des ports A, B, F et des signaux internes S1 et S2 durant une simulation comprise entre les temps 0 ns jusqu'à 25 ns.

#### **EXERCICE 4:**

Dans le code VHDL suivant, indiquez les quatre erreurs détectées au moment de la compilation. Pour chaque ligne comportant une erreur, donnez le code corrigé correspondant. library ieee;

```

use ieee.std logic 1164.all;

use ieee.numeric_std.all;

entity unite arithmetique is

```

generic (W: positive := 8);

A, B: in integer(W - 1 downto o);

choix: in std logic vector(2 downto 0);

end unite arithmetique;

architecture arch of unite\_arithmetique is

begin

process(A, B, choix)

variable t : integer range o to 2\*\*W-1;

port(

$t \le to integer(A * B);$

case to integer(unsigned(choix)) is

-- largeur des opérandes

-- les operandes de type signé -- le sélecteur d'opération

F: out std logic vector(W - 1 downto o)); -- le résultat

when  $4 \Rightarrow F \le \text{std logic vector(abs(A))};$

when 6 => F <= t;

when others  $\Rightarrow$  F  $\leq$  'X';

end case: end process: end arch;

#### **TRAVAUX DIRIGES 4 (1H30)**

## Exercice 5:

```

a. Dessinez le système représenté par le programme VHDL suivant :

library IEEE;

architecture bev of exo5 is

use IEEE.std logic 1164.all;

signal local: std_logic;

entity exo5 is

begin

port (a, b, c, d, clk: in std logic;

local <= '1' when ((a='1' and b='1') or

q : out std_logic);

c = '1'

end exo5;

else '0';

process (clk, local)

b. Ecrivez un programme équivalent à l'aide

begin

d'un seul processus

if local='1' then

q \le '0';

elsif clk'event and clk='1' then

q \le d;

Exercice 6:

end if;

Soit le code VHDL suivant.

end process;

library IEEE;

end;

use IEEE.std logic 1164.all;

entity exo_1 is

port (A, B, C: in std logic;

Q1, Q2 : out std_logic);

end exo 1;

architecture synth of exo 1 is

signal V, R: std logic;

begin

process (V, C)

begin

if (V='1') then

Q2 \leq C;

end if;

end process;

R \leq B xor C;

process (A)

Ω2 -----

begin

if (A'event and A='1') then

Figure.1: Chronogramme de l'exercice 6

Q1 <= C;

V \leq R;

end if:

end process:

end synth;

```

Dessiner le système représenté par ce code. Compléter le diagramme des temps de la figure 1.

## UNIVERSITÉ DE BOUMERDES MASTER 1 INFOTRONIQUE SEMESTRE 2

# DEPARTEMENT D'INFOTRONIQUE SYSTEMES NUMERIQUES COMPLEXES

## **TRAVAUX DIRIGES 4 (1H30)**